# INTEGRATED CIRCUITS

# DATA SHEET

# TDA8754 Triple 8-bit video ADC up to 270 Msps

Preliminary specification Supersedes data of 2003 Jul 16 2003 Sep 30

**TDA8754**

| CONTE          | NTS                                       | 9.8          | Phase register                                              |

|----------------|-------------------------------------------|--------------|-------------------------------------------------------------|

| 1              | FEATURES                                  | 9.9<br>9.10  | PLL divider registers Horizontal sync registers             |

| 2              | APPLICATIONS                              | 9.11         | Coast register                                              |

| 3              | GENERAL DESCRIPTION                       | 9.12         | Horizontal sync selection register                          |

|                |                                           | 9.13         | Vertical sync selection register                            |

| 4              | QUICK REFERENCE DATA                      | 9.14         | Clamp register                                              |

| 5              | ORDERING INFORMATION                      | 9.15<br>9.16 | Inverter register                                           |

| 6              | BLOCK DIAGRAM                             | 9.16<br>9.17 | Output register Output enable register 1                    |

| 7              | PINNING                                   | 9.17         | Output enable register 2                                    |

| 7.1            | LQFP144 package                           | 9.19         | Clock output register                                       |

| 7.2            | LBGA208 package                           | 9.20         | Internal oscillator register                                |

| 8              | FUNCTIONAL DESCRIPTION                    | 9.21         | Power management register                                   |

| 8.1            | Power management                          | 9.22         | Read register                                               |

| 8.1.1          | Standby mode                              | 9.23         | Version register                                            |

| 8.1.2          | Power-down mode                           | 9.24<br>9.25 | Sign detection register Activity detection register 1       |

| 8.2            | Analog video input                        | 9.26         | Activity detection register 1 Activity detection register 2 |

| 8.2.1          | Analog multiplexers                       | 10           | LIMITING VALUES                                             |

| 8.2.2          | Activity detection ADC                    |              |                                                             |

| 8.2.3<br>8.2.4 | Clamp                                     | 11           | THERMAL CHARACTERISTICS                                     |

| 8.2.5          | AGC                                       | 12           | CHARACTERISTICS                                             |

| 8.3            | HSOSEL, DEO and SCHCKREFO                 | 13           | TIMING                                                      |

| 8.4            | PLL                                       | 14           | APPLICATION INFORMATION                                     |

| 8.5            | Sync-on-green                             | 15           | PACKAGE OUTLINES                                            |

| 8.6            | Programmable coast                        | 16           | SOLDERING                                                   |

| 8.7            | Data enable                               | 16.1         | Introduction to soldering surface mount                     |

| 8.8<br>8.9     | Sync separator<br>3-level                 | 10.1         | packages                                                    |

|                |                                           | 16.2         | Reflow soldering                                            |

| 9              | I <sup>2</sup> C-BUS REGISTER DESCRIPTION | 16.3         | Wave soldering                                              |

| 9.1            | I <sup>2</sup> C-bus formats              | 16.4         | Manual soldering                                            |

| 9.1.1<br>9.1.2 | Write 1 register Write all registers      | 16.5         | Suitability of surface mount IC packages for                |

| 9.1.3          | Read register                             |              | wave and reflow soldering methods                           |

| 9.2            | I <sup>2</sup> C-bus registers overview   | 17           | DATA SHEET STATUS                                           |

| 9.3            | Offset registers (R, G and B)             | 18           | DEFINITIONS                                                 |

| 9.4            | Coarse registers (R, G and B)             | 19           | DISCLAIMERS                                                 |

| 9.5            | Fine registers (R, G and B)               | 20           | PURCHASE OF PHILIPS I2C COMPONENTS                          |

| 9.6            | SOG register                              |              |                                                             |

| 9.7            | PLL control                               |              |                                                             |

2

TDA8754

#### 1 FEATURES

- 3.3 V power supply

- Triple 8-bit ADC

- Analog sampling rate from 12 up to 270 Msps

- · Maximum data rate:

- Single port mode: 140 MHz

- Dual port mode: 270 MHz

- 3.3 V LV-TTL outputs.

- PLL control via I<sup>2</sup>C-bus:

- Low PLL drift with temperature (2 phase steps maximum)

- PLL generates the ADC sampling clock which can be locked on the line frequency from 15 to 150 kHz

- Integrated PLL divider

- Programmable phase clock adjustment cells.

- Three clamp circuits for programming a clamp code from –24 to +136 by steps of 1 LSB (mid-scale clamping for YUV signal)

- · Internal generation of clamp signal

- Three independent blanking functions

- Input:

- 410 MHz analog bandwidth

- Two independent analog inputs selectable via I<sup>2</sup>C-bus

- Analog input from 0.5 to 1 V (p-p) to produce a full-scale ADC input of 1 V (p-p)

- Three controllable amplifiers: gain control via I<sup>2</sup>C-bus to produce full-scale peak-to-peak output with a half LSB resolution.

- Synchronisation:

- Frame and field detection for interlaced video signal

- Parasite synchronization pulse detection and suppression

- Sync processing for composite sync, 3-level sync and sync-on-green signals

- Polarity and activity detection.

- IC control via I<sup>2</sup>C-bus serial interface

- Power-down mode.

#### 2 APPLICATIONS

- RGB/YUV high-speed digitizing

- · LCD panels drive

- LCD projection system

- New TV concept.

#### 3 GENERAL DESCRIPTION

The TDA8754 is a complete triple 8-bit ADC with an integrated PLL running up to 270 Msps and analog preprocessing functions (clamp and PGA) optimized for capturing RGB/YUV graphic signals.

The PLL generates a pixel clock from inputs HSYNC and COAST.

The TDA8754 offers full sync processing for sync-on-green applications. A clamp signal may be generated internally or provided externally.

The clamp levels, gains and other settings are controlled via the I<sup>2</sup>C-bus interface.

This IC supports display resolutions up to QXGA (2048  $\times$  1536) at 85 Hz.

# Triple 8-bit video ADC up to 270 Msps

TDA8754

#### 4 QUICK REFERENCE DATA

| SYMBOL           | PARAMETER                  | CONDITIONS                                          | MIN. | TYP.  | MAX. | UNIT |

|------------------|----------------------------|-----------------------------------------------------|------|-------|------|------|

| V <sub>CCA</sub> | analog supply voltage      |                                                     | 3.0  | 3.3   | 3.6  | V    |

| V <sub>CCD</sub> | digital supply voltage     |                                                     | 3.0  | 3.3   | 3.6  | V    |

| V <sub>CCO</sub> | output supply voltage      |                                                     | 3.0  | 3.3   | 3.6  | V    |

| f <sub>PLL</sub> | analog PLL frequency       |                                                     | 12   | _     | 270  | MHz  |

| ENOB             | effective number of bits   | f <sub>clk</sub> = 270 MHz; f <sub>i</sub> = 10 MHz | _    | 7.6   | _    | bits |

| INL              | integral non-linearity     | f <sub>clk</sub> = 270 MHz; f <sub>i</sub> = 10 MHz | _    | ±0.6  | ±1.3 | LSB  |

| DNL              | differential non-linearity | f <sub>clk</sub> = 270 MHz; f <sub>i</sub> = 10 MHz | _    | ±0.25 | ±0.6 | LSB  |

| P <sub>tot</sub> | power dissipation          |                                                     | _    | 1     | 1.3  | W    |

#### 5 ORDERING INFORMATION

| TYPE         |                        | SAMPLING                                     |          |           |

|--------------|------------------------|----------------------------------------------|----------|-----------|

| NUMBER       | NAME                   | DESCRIPTION                                  | VERSION  | FREQUENCY |

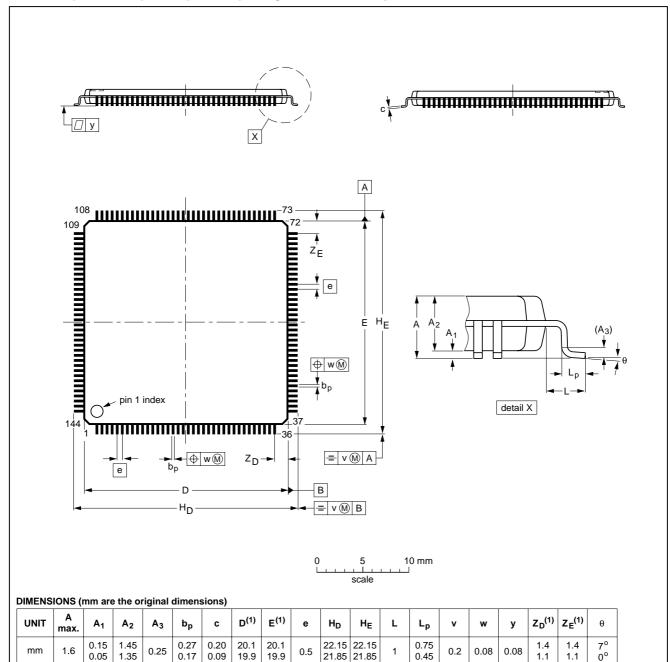

| TDA8754HL/11 | LQFP144                | plastic low profile quad flat package;       | SOT486-1 | 110 MHz   |

| TDA8754HL/14 |                        | 144 leads; body 20 × 20 × 1.4 mm             |          | 140 MHz   |

| TDA8754HL/17 |                        |                                              |          | 170 MHz   |

| TDA8754HL/21 |                        |                                              |          | 210 MHz   |

| TDA8754HL/25 |                        |                                              |          | 250 MHz   |

| TDA8754HL/27 |                        |                                              |          | 270 MHz   |

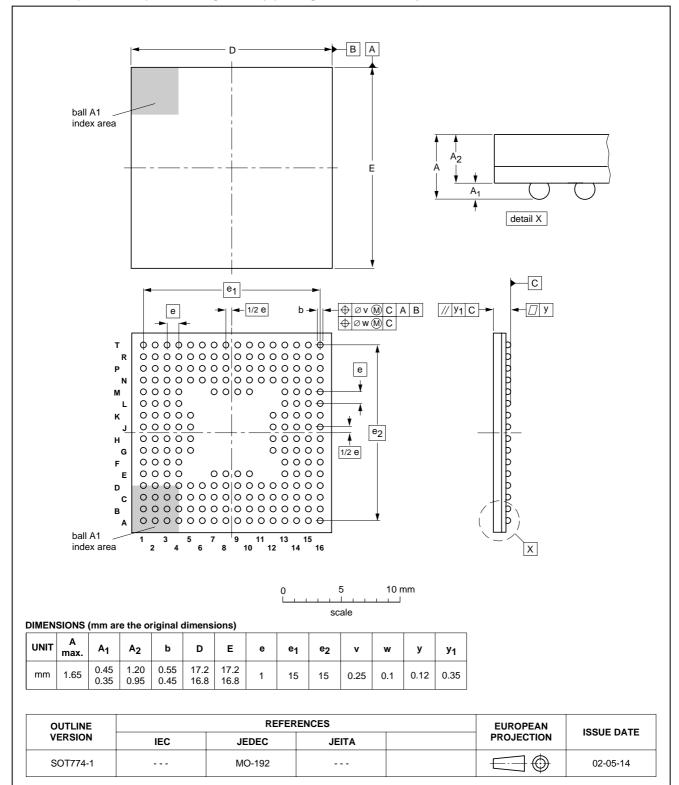

| TDA8754EL/11 | LBGA208 <sup>(1)</sup> | plastic low profile ball grid array package; | SOT774-1 | 110 MHz   |

| TDA8754EL/14 |                        | 208 balls; body 17 × 17 × 1.05 mm            |          | 140 MHz   |

| TDA8754EL/17 |                        |                                              |          | 170 MHz   |

| TDA8754EL/21 |                        |                                              |          | 210 MHz   |

| TDA8754EL/25 |                        |                                              |          | 250 MHz   |

| TDA8754EL/27 |                        |                                              |          | 270 MHz   |

#### Note

1. Values are not yet guarantee.

#### TDA8754

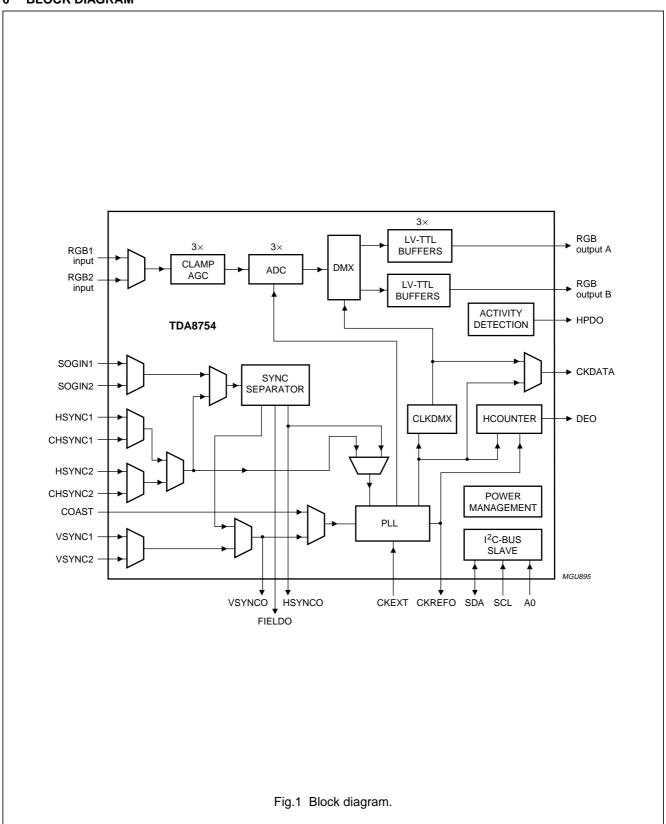

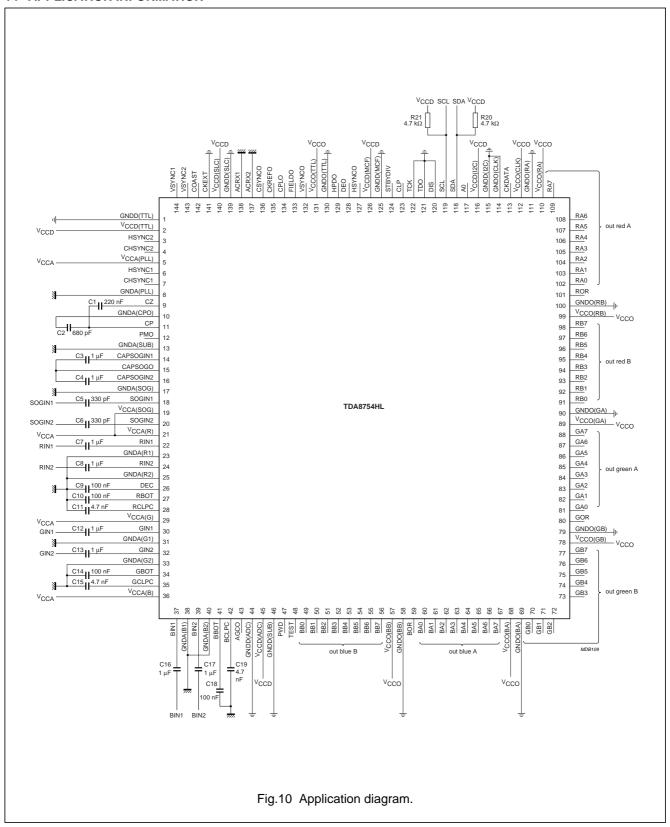

#### **6 BLOCK DIAGRAM**

5

2003 Sep 30

TDA8754

#### 7 PINNING

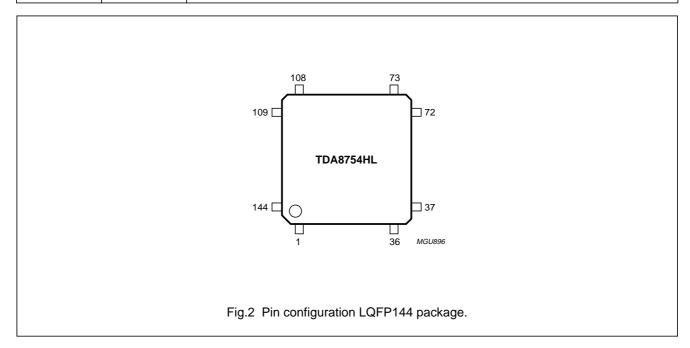

#### 7.1 LQFP144 package

| GNDD(TTL)         1         TTL input digital ground           VCCDITTU         2         TTL input digital supply voltage           HSYNC2         3         horizontal synchronization pulse input 2           CHSYNC2         4         composite horizontal synchronization pulse input 2           VCCAIPLLI         5         PLL analog supply voltage           HSYNC1         6         horizontal synchronization pulse input 1           CHSYNC1         7         composite horizontal synchronization pulse input 1           GNDA(PLLI)         8         PLL analog ground           CZ         9         PLL filter input           GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGIN1         14         decoupling SOG input 2           CAPSOGIN2         16         decoupling SOG input 2           CAPSOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN1         18         sync-on-green inpu                                                  | SYMBOL                | PIN | DESCRIPTION                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|----------------------------------------------------|

| HSYNC2         3         horizontal synchronization pulse input 2           CHSYNC2         4         composite horizontal synchronization pulse input 2           VCCA(PLL)         5         PLL analog supply voltage           HSYNC1         7         composite horizontal synchronization pulse input 1           CHSYNC1         7         composite horizontal synchronization pulse input 1           GNDA(PLL)         8         PLL filter input           GNDA(PDC)         10         CPO analog ground           CZ         9         PLL filter input           GNDA(PO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGIN1         14         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog supply voltage           SOGIN1         18         sync-on-green input 1           VccA(soc)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2                                                       | GNDD(TTL)             | 1   | TTL input digital ground                           |

| CHSYNC2         4         composite horizontal synchronization pulse input 2           VCCA(PLL)         5         PLL analog supply voltage           HSYNC1         6         horizontal synchronization pulse input 1           CHSYNC1         7         composite horizontal synchronization pulse input 1           GNDA(PLL)         8         PLL analog ground           CZ         9         PLL filter input           GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGIN1         14         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VccA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog input 1           GNDA(R1)         23         red channel analog input 1           GNDA(R1)         23         red channel analog input 2                                                                           | V <sub>CCD(TTL)</sub> | 2   | TTL input digital supply voltage                   |

| VccA(PLL)         5         PLL analog supply voltage           HSYNC1         6         horizontal synchronization pulse input 1           CHSYNC1         7         composite horizontal synchronization pulse input 1           GNDA(PLL)         8         PLL analog ground           CZ         9         PLL filter input           GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGIN1         14         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VccA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VccA(R)         21         red channel analog supply voltage           RIN1         22         red channel analog supply voltage           RIN1         23         red channel analog input 1           GNDA(                                                                           | HSYNC2                | 3   | horizontal synchronization pulse input 2           |

| HSYNC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHSYNC2               | 4   | composite horizontal synchronization pulse input 2 |

| CHSYNC1         7         composite horizontal synchronization pulse input 1           GNDA(PLL)         8         PLL analog ground           CZ         9         PLL filter input           GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGIN2         16         decoupling SOG input 2           CAPSOGIN2         16         decoupling SOG input 2           SOBNA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VccA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VccA(R)         21         red channel analog supply voltage           RIN1         22         red channel analog input 1           RIN2         24         red channel analog input 2           GNDA(R2)         25         red channel analog input 2           GNDA(R2)         25         red channel analog input 3           REC <td< td=""><td>V<sub>CCA(PLL)</sub></td><td>5</td><td>PLL analog supply voltage</td></td<> | V <sub>CCA(PLL)</sub> | 5   | PLL analog supply voltage                          |

| GNDA(PLL)         8         PLL analog ground           CZ         9         PLL filter input           GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog supply voltage           RIM1         22         red channel analog input 1           GNDA(R1)         23         red channel analog input 2           GNDA(R2)         25         red channel analog ground           DEC         26         main regulator decoupling input           RCLPC         28         red channel clamp capacitor input           VCCA(G)         29                                                                                                | HSYNC1                | 6   | horizontal synchronization pulse input 1           |

| CZ         9         PLL filter input           GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGIN2         16         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VccA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VcCA(R)         21         red channel analog supply voltage           SOGIN2         20         sync-on-green input 2           VcCA(R)         21         red channel analog supply voltage           RIN1         22         red channel analog supply voltage           RIN1         23         red channel analog input 2           GNDA(R2)         25         red channel analog ground           REC         26         main regulator decoupling input           RCLPC         28                                                                                         | CHSYNC1               | 7   | composite horizontal synchronization pulse input 1 |

| GNDA(CPO)         10         CPO analog ground           CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           Vcca(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VccA(R)         21         red channel analog supply voltage           RIM1         22         red channel analog input 1           GNDA(R1)         23         red channel analog input 2           GNDA(R2)         25         red channel 2 analog ground           RIN2         24         red channel 2 analog ground           DEC         26         main regulator decoupling input           RCLPC         28         red channel analog supply voltage           GIN1         30         green channel analog supply voltage           GIN1                                                                                | GNDA(PLL)             | 8   | PLL analog ground                                  |

| CP         11         PLL filter input           PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGINI         14         decoupling SOG input 1           CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           CNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog supply voltage           RIN1         22         red channel analog input 1           GNDA(R1)         23         red channel analog ground           RIN2         24         red channel analog input 2           RNDA(R2)         25         red channel 2 analog ground           DEC         26         main regulator decoupling input           RCLPC         28         red channel analog supply voltage           GIN1         30         green channel analog input 1           GNDA(G1)         31         green channel analog input 2           GNDA(G2)                                                                           | CZ                    | 9   | PLL filter input                                   |

| PMO         12         phase measurement output (test)           GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog supply voltage           RIN1         22         red channel analog input 1           GNDA(R1)         23         red channel analog ground           RIN2         24         red channel 2 analog ground           DEC         26         main regulator decoupling input           RBOT         27         red channel ladder decoupling input           RCLPC         28         red channel clamp capacitor input           VCCA(G)         29         green channel analog supply voltage           GIN1         30         green channel 1 analog ground           GNDA(G2)         31         green channel 2 analog ground <td>GNDA(CPO)</td> <td>10</td> <td>CPO analog ground</td>     | GNDA(CPO)             | 10  | CPO analog ground                                  |

| GNDA(SUB)         13         SUB analog ground           CAPSOGIN1         14         decoupling SOG input 1           CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog supply voltage           RIM1         22         red channel analog input 1           GNDA(R1)         23         red channel analog ground           RIN2         24         red channel analog input 2           GNDA(R2)         25         red channel 2 analog ground           DEC         26         main regulator decoupling input           RBOT         27         red channel ladder decoupling input           RCLPC         28         red channel clamp capacitor input           V <sub>CCA(G)</sub> 29         green channel analog supply voltage           GIN1         30         green channel analog input 1           GNDA(G1)         31         green channel analog ground                                                              | СР                    | 11  | PLL filter input                                   |

| CAPSOGIN1         14         decoupling SOG input 1           CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog supply voltage           RIM1         22         red channel analog input 1           GNDA(R1)         23         red channel analog ground           RIN2         24         red channel analog input 2           GNDA(R2)         25         red channel 2 analog ground           DEC         26         main regulator decoupling input           RBOT         27         red channel adecoupling input           RCLPC         28         red channel analog supply voltage           GIN1         30         green channel analog input 1           GNDA(G1)         31         green channel analog input 2           GNDA(G2)         33         green channel analog input 2           GNDA(G2)         33         green channel 2 analog ground                                                                  | PMO                   | 12  | phase measurement output (test)                    |

| CAPSOGO         15         decoupling SOG output           CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           VCCA(SOG)         19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           VCCA(R)         21         red channel analog supply voltage           RIM1         22         red channel analog input 1           GNDA(R1)         23         red channel 1 analog ground           RIN2         24         red channel analog input 2           GNDA(R2)         25         red channel 2 analog ground           DEC         26         main regulator decoupling input           REOT         27         red channel adecoupling input           RCLPC         28         red channel analog supply voltage           GIN1         30         green channel analog input 1           GNDA(G1)         31         green channel analog input 2           GNDA(G2)         33         green channel analog input 2           GNDA(G2)         33         green channel analog input 2           GNDA(G2)         34         green channel analog input 2     <                                                      | GNDA(SUB)             | 13  | SUB analog ground                                  |

| CAPSOGIN2         16         decoupling SOG input 2           GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           V <sub>CCA(SOG)</sub> 19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           V <sub>CCA(R)</sub> 21         red channel analog supply voltage           RIN1         22         red channel analog input 1           GNDA(R1)         23         red channel 1 analog ground           RIN2         24         red channel analog input 2           GNDA(R2)         25         red channel 2 analog ground           DEC         26         main regulator decoupling input           RBOT         27         red channel ladder decoupling input           RCLPC         28         red channel clamp capacitor input           V <sub>CCA(G)</sub> 29         green channel analog supply voltage           GIN1         30         green channel analog input 1           GNDA(G1)         31         green channel analog input 2           GNDA(G2)         33         green channel 2 analog ground           GBOT         34         green channel ladder decoupling input           GCLPC         35         green chan                                           | CAPSOGIN1             | 14  | decoupling SOG input 1                             |

| GNDA(SOG)         17         SOG analog ground           SOGIN1         18         sync-on-green input 1           V <sub>CCA(SOG)</sub> 19         SOG analog supply voltage           SOGIN2         20         sync-on-green input 2           V <sub>CCA(R)</sub> 21         red channel analog supply voltage           RIN1         22         red channel analog input 1           GNDA(R1)         23         red channel 1 analog ground           RIN2         24         red channel analog input 2           GNDA(R2)         25         red channel 2 analog ground           DEC         26         main regulator decoupling input           RBOT         27         red channel ladder decoupling input           RCLPC         28         red channel clamp capacitor input           V <sub>CCA(G)</sub> 29         green channel analog supply voltage           GIN1         30         green channel analog input 1           GNDA(G1)         31         green channel analog ground           GIN2         32         green channel analog input 2           GNDA(G2)         33         green channel 2 analog ground           GBOT         34         green channel ladder decoupling input           GCLPC         35         green chan                                           | CAPSOGO               | 15  | decoupling SOG output                              |

| SOGIN1       18       sync-on-green input 1         VCCA(SOG)       19       SOG analog supply voltage         SOGIN2       20       sync-on-green input 2         VCCA(R)       21       red channel analog supply voltage         RIN1       22       red channel analog input 1         GNDA(R1)       23       red channel analog ground         RIN2       24       red channel analog input 2         GNDA(R2)       25       red channel 2 analog ground         DEC       26       main regulator decoupling input         RBOT       27       red channel ladder decoupling input         RCLPC       28       red channel clamp capacitor input         VCCA(G)       29       green channel analog supply voltage         GIN1       30       green channel analog input 1         GNDA(G1)       31       green channel 1 analog ground         GIN2       32       green channel analog input 2         GNDA(G2)       33       green channel 2 analog ground         GBOT       34       green channel ladder decoupling input         GCLPC       35       green channel clamp capacitor input         V <sub>CCA(B)</sub> 36       blue channel analog input 1                                                                                                                                | CAPSOGIN2             | 16  | decoupling SOG input 2                             |

| VCCA(SOG)       19       SOG analog supply voltage         SOGIN2       20       sync-on-green input 2         VCCA(R)       21       red channel analog supply voltage         RIN1       22       red channel analog input 1         GNDA(R1)       23       red channel analog ground         RIN2       24       red channel analog input 2         GNDA(R2)       25       red channel 2 analog ground         DEC       26       main regulator decoupling input         RBOT       27       red channel ladder decoupling input         RCLPC       28       red channel clamp capacitor input         VCCA(G)       29       green channel analog supply voltage         GIN1       30       green channel analog input 1         GNDA(G1)       31       green channel 1 analog ground         GIN2       32       green channel analog input 2         GNDA(G2)       33       green channel 2 analog ground         GBOT       34       green channel ladder decoupling input         GCLPC       35       green channel clamp capacitor input         V <sub>CCA(B)</sub> 36       blue channel analog input 1                                                                                                                                                                                    | GNDA(SOG)             | 17  | SOG analog ground                                  |

| SOGIN2 20 sync-on-green input 2  V <sub>CCA(R)</sub> 21 red channel analog supply voltage  RIN1 22 red channel analog input 1  GNDA(R1) 23 red channel 1 analog ground  RIN2 24 red channel analog input 2  GNDA(R2) 25 red channel 2 analog ground  DEC 26 main regulator decoupling input  RBOT 27 red channel ladder decoupling input  RCLPC 28 red channel clamp capacitor input  V <sub>CCA(G)</sub> 29 green channel analog supply voltage  GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel 2 analog ground  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog supply voltage  BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SOGIN1                | 18  | sync-on-green input 1                              |

| V <sub>CCA(R)</sub> 21     red channel analog supply voltage       RIN1     22     red channel analog input 1       GNDA(R1)     23     red channel 1 analog ground       RIN2     24     red channel analog input 2       GNDA(R2)     25     red channel 2 analog ground       DEC     26     main regulator decoupling input       RBOT     27     red channel ladder decoupling input       RCLPC     28     red channel clamp capacitor input       V <sub>CCA(G)</sub> 29     green channel analog supply voltage       GIN1     30     green channel analog input 1       GNDA(G1)     31     green channel 1 analog ground       GIN2     32     green channel 2 analog ground       GNDA(G2)     33     green channel 2 analog ground       GBOT     34     green channel ladder decoupling input       GCLPC     35     green channel clamp capacitor input       V <sub>CCA(B)</sub> 36     blue channel analog supply voltage       BIN1     37     blue channel analog input 1                                                                                                                                                                                                                                                                                                                   | V <sub>CCA(SOG)</sub> | 19  | SOG analog supply voltage                          |

| RIN1 22 red channel analog input 1 GNDA(R1) 23 red channel 1 analog ground RIN2 24 red channel analog input 2 GNDA(R2) 25 red channel 2 analog ground DEC 26 main regulator decoupling input RBOT 27 red channel ladder decoupling input RCLPC 28 red channel clamp capacitor input VCCA(G) 29 green channel analog supply voltage GIN1 30 green channel analog input 1 GNDA(G1) 31 green channel 1 analog ground GIN2 32 green channel analog input 2 GNDA(G2) 33 green channel 2 analog ground GBOT 34 green channel ladder decoupling input GCLPC 35 green channel clamp capacitor input VCCA(B) 36 blue channel analog supply voltage BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       | 20  | sync-on-green input 2                              |

| GNDA(R1) 23 red channel 1 analog ground RIN2 24 red channel analog input 2 GNDA(R2) 25 red channel 2 analog ground DEC 26 main regulator decoupling input RBOT 27 red channel ladder decoupling input RCLPC 28 red channel clamp capacitor input VCCA(G) 29 green channel analog supply voltage GIN1 30 green channel analog input 1 GNDA(G1) 31 green channel 1 analog ground GIN2 32 green channel analog input 2 GNDA(G2) 33 green channel 2 analog ground GBOT 34 green channel ladder decoupling input GCLPC 35 green channel clamp capacitor input VCCA(B) 36 blue channel analog supply voltage BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>CCA(R)</sub>   | 21  | red channel analog supply voltage                  |

| RIN2 24 red channel analog input 2 GNDA(R2) 25 red channel 2 analog ground  DEC 26 main regulator decoupling input  RBOT 27 red channel ladder decoupling input  RCLPC 28 red channel clamp capacitor input  V <sub>CCA(G)</sub> 29 green channel analog supply voltage  GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog input 1  blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RIN1                  | 22  | red channel analog input 1                         |

| GNDA(R2) 25 red channel 2 analog ground  DEC 26 main regulator decoupling input  RBOT 27 red channel ladder decoupling input  RCLPC 28 red channel clamp capacitor input  V <sub>CCA(G)</sub> 29 green channel analog supply voltage  GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GNDA(R1)              | 23  | red channel 1 analog ground                        |

| DEC 26 main regulator decoupling input  RBOT 27 red channel ladder decoupling input  RCLPC 28 red channel clamp capacitor input  V <sub>CCA(G)</sub> 29 green channel analog supply voltage  GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RIN2                  | 24  | red channel analog input 2                         |

| RBOT 27 red channel ladder decoupling input  RCLPC 28 red channel clamp capacitor input  V <sub>CCA(G)</sub> 29 green channel analog supply voltage  GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog supply voltage  BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GNDA(R2)              | 25  | red channel 2 analog ground                        |

| RCLPC 28 red channel clamp capacitor input  V <sub>CCA(G)</sub> 29 green channel analog supply voltage  GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog supply voltage  BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DEC                   | 26  | main regulator decoupling input                    |

| V <sub>CCA(G)</sub> 29       green channel analog supply voltage         GIN1       30       green channel analog input 1         GNDA(G1)       31       green channel 1 analog ground         GIN2       32       green channel analog input 2         GNDA(G2)       33       green channel 2 analog ground         GBOT       34       green channel ladder decoupling input         GCLPC       35       green channel clamp capacitor input         V <sub>CCA(B)</sub> 36       blue channel analog supply voltage         BIN1       37       blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RBOT                  | 27  | red channel ladder decoupling input                |

| GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog supply voltage  BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RCLPC                 | 28  | red channel clamp capacitor input                  |

| GIN1 30 green channel analog input 1  GNDA(G1) 31 green channel 1 analog ground  GIN2 32 green channel analog input 2  GNDA(G2) 33 green channel 2 analog ground  GBOT 34 green channel ladder decoupling input  GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog supply voltage  BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>CCA(G)</sub>   | 29  | green channel analog supply voltage                |

| GIN2 32 green channel analog input 2 GNDA(G2) 33 green channel 2 analog ground GBOT 34 green channel ladder decoupling input GCLPC 35 green channel clamp capacitor input V <sub>CCA(B)</sub> 36 blue channel analog supply voltage BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       | 30  | green channel analog input 1                       |

| GNDA(G2) 33 green channel 2 analog ground GBOT 34 green channel ladder decoupling input GCLPC 35 green channel clamp capacitor input V <sub>CCA(B)</sub> 36 blue channel analog supply voltage BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GNDA(G1)              | 31  | green channel 1 analog ground                      |

| GBOT 34 green channel ladder decoupling input GCLPC 35 green channel clamp capacitor input V <sub>CCA(B)</sub> 36 blue channel analog supply voltage BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GIN2                  | 32  | green channel analog input 2                       |

| GCLPC 35 green channel clamp capacitor input  V <sub>CCA(B)</sub> 36 blue channel analog supply voltage  BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GNDA(G2)              | 33  | green channel 2 analog ground                      |

| V <sub>CCA(B)</sub> 36     blue channel analog supply voltage       BIN1     37     blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GBOT                  | 34  | green channel ladder decoupling input              |

| BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GCLPC                 | 35  | green channel clamp capacitor input                |

| BIN1 37 blue channel analog input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>CCA(B)</sub>   | 36  | blue channel analog supply voltage                 |

| GNDA(B1) 38 blue channel 1 analog ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       | 37  | blue channel analog input 1                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GNDA(B1)              | 38  | blue channel 1 analog ground                       |

TDA8754

| SYMBOL                | PIN | DESCRIPTION                              |

|-----------------------|-----|------------------------------------------|

| BIN2                  | 39  | blue channel analog input 2              |

| GNDA(B2)              | 40  | blue channel 2 analog ground             |

| BBOT                  | 41  | blue channel ladder decoupling input     |

| BCLPC                 | 42  | blue channel clamp capacitor input       |

| AGCO                  | 43  | AGC output                               |

| GNDD(ADC)             | 44  | ADC digital ground                       |

| V <sub>CCD(ADC)</sub> | 45  | ADC digital supply voltage               |

| GNDD(SUB)             | 46  | SUB digital ground                       |

| PWD                   | 47  | power-down control input                 |

| TEST                  | 48  | test input; must be connected to ground  |

| BB0                   | 49  | blue channel ADC output B bit 0          |

| BB1                   | 50  | blue channel ADC output B bit 1          |

| BB2                   | 51  | blue channel ADC output B bit 2          |

| BB3                   | 52  | blue channel ADC output B bit 3          |

| BB4                   | 53  | blue channel ADC output B bit 4          |

| BB5                   | 54  | blue channel ADC output B bit 5          |

| BB6                   | 55  | blue channel ADC output B bit 6          |

| BB7                   | 56  | blue channel ADC output B bit 7          |

| V <sub>CCO(BB)</sub>  | 57  | blue channel B output supply voltage     |

| GNDO(BB)              | 58  | blue channel B output ground             |

| BOR                   | 59  | blue channel ADC output bit out of range |

| BA0                   | 60  | blue channel ADC output A bit 0          |

| BA1                   | 61  | blue channel ADC output A bit 1          |

| BA2                   | 62  | blue channel ADC output A bit 2          |

| BA3                   | 63  | blue channel ADC output A bit 3          |

| BA4                   | 64  | blue channel ADC output A bit 4          |

| BA5                   | 65  | blue channel ADC output A bit 5          |

| BA6                   | 66  | blue channel ADC output A bit 6          |

| BA7                   | 67  | blue channel ADC output A bit 7          |

| V <sub>CCO(BA)</sub>  | 68  | blue channel A output supply voltage     |

| GNDO(BA)              | 69  | blue channel A output ground             |

| GB0                   | 70  | green channel ADC output B bit 0         |

| GB1                   | 71  | green channel ADC output B bit 1         |

| GB2                   | 72  | green channel ADC output B bit 2         |

| GB3                   | 73  | green channel ADC output B bit 3         |

| GB4                   | 74  | green channel ADC output B bit 4         |

| GB5                   | 75  | green channel ADC output B bit 5         |

| GB6                   | 76  | green channel ADC output B bit 6         |

| GB7                   | 77  | green channel ADC output B bit 7         |

| V <sub>CCO(GB)</sub>  | 78  | green channel B output supply voltage    |

| GNDO(GB)              | 79  | green channel B output ground            |

TDA8754

| SYMBOL                | PIN | DESCRIPTION                                       |

|-----------------------|-----|---------------------------------------------------|

| GOR                   | 80  | green channel ADC output bit out of range         |

| GA0                   | 81  | green channel ADC output A bit 0                  |

| GA1                   | 82  | green channel ADC output A bit 1                  |

| GA2                   | 83  | green channel ADC output A bit 2                  |

| GA3                   | 84  | green channel ADC output A bit 3                  |

| GA4                   | 85  | green channel ADC output A bit 4                  |

| GA5                   | 86  | green channel ADC output A bit 5                  |

| GA6                   | 87  | green channel ADC output A bit 6                  |

| GA7                   | 88  | green channel ADC output A bit 7                  |

| V <sub>CCO(GA)</sub>  | 89  | green channel A output supply voltage             |

| GNDO(GA)              | 90  | green channel A output ground                     |

| RB0                   | 91  | red channel ADC output B bit 0                    |

| RB1                   | 92  | red channel ADC output B bit 1                    |

| RB2                   | 93  | red channel ADC output B bit 2                    |

| RB3                   | 94  | red channel ADC output B bit 3                    |

| RB4                   | 95  | red channel ADC output B bit 4                    |

| RB5                   | 96  | red channel ADC output B bit 5                    |

| RB6                   | 97  | red channel ADC output B bit 6                    |

| RB7                   | 98  | red channel ADC output B bit 7                    |

| V <sub>CCO(RB)</sub>  | 99  | red channel B output supply voltage               |

| GNDO(RB)              | 100 | red channel B output ground                       |

| ROR                   | 101 | red channel ADC output bit out of range           |

| RA0                   | 102 | red channel ADC output A bit 0                    |

| RA1                   | 103 | red channel ADC output A bit 1                    |

| RA2                   | 104 | red channel ADC output A bit 2                    |

| RA3                   | 105 | red channel ADC output A bit 3                    |

| RA4                   | 106 | red channel ADC output A bit 4                    |

| RA5                   | 107 | red channel ADC output A bit 5                    |

| RA6                   | 108 | red channel ADC output A bit 6                    |

| RA7                   | 109 | red channel ADC output A bit 7                    |

| V <sub>CCO(RA)</sub>  | 110 | red channel A output supply voltage               |

| GNDO(RA)              | 111 | red channel A output ground                       |

| V <sub>CCO(CLK)</sub> | 112 | clock output digital supply voltage               |

| CKDATA                | 113 | data clock output                                 |

| GNDO(CLK)             | 114 | clock output digital ground                       |

| GNDD(I2C)             | 115 | I <sup>2</sup> C-bus lines digital ground         |

| V <sub>CCD(I2C)</sub> | 116 | I <sup>2</sup> C-bus lines digital supply voltage |

| A0                    | 117 | I <sup>2</sup> C-bus address control input        |

| SDA                   | 118 | I <sup>2</sup> C-bus serial data input and output |

| SCL                   | 119 | I <sup>2</sup> C-bus serial clock input           |

| DIS                   | 120 | I <sup>2</sup> C-bus disable control input        |

Preliminary specification

# Triple 8-bit video ADC up to 270 Msps

Philips Semiconductors

# TDA8754

| SYMBOL                | PIN | DESCRIPTION                                                       |

|-----------------------|-----|-------------------------------------------------------------------|

| TDO                   | 121 | scan test output                                                  |

| TCK                   | 122 | scan test mode input; must be connected to ground                 |

| CLP                   | 123 | clamp pulse input                                                 |

| STBYDIV               | 124 | DVI standby output                                                |

| GNDD(MCF)             | 125 | MCF digital ground                                                |

| V <sub>CCD(MCF)</sub> | 126 | MCF digital supply voltage                                        |

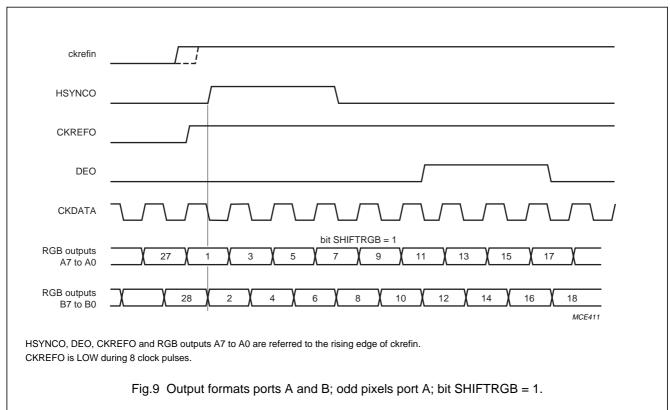

| HSYNCO                | 127 | horizontal synchronization pulse output                           |

| DEO                   | 128 | data enable output                                                |

| HPDO                  | 129 | hot plug detector output                                          |

| GNDO(TTL)             | 130 | TTL output digital ground                                         |

| V <sub>CCO(TTL)</sub> | 131 | TTL output digital supply voltage                                 |

| VSYNCO                | 132 | vertical synchronization pulse output                             |

| FIELDO                | 133 | field information output                                          |

| CLPO                  | 134 | clamp output                                                      |

| CKREFO                | 135 | reference output clock; re-synchronized horizontal negative pulse |

| CSYNCO                | 136 | composite synchronization output                                  |

| ACRX2                 | 137 | test pin; should be connected to ground                           |

| ACRX1                 | 138 | test pin; should be connected to ground                           |

| GNDD(SLC)             | 139 | SLC digital ground                                                |

| V <sub>CCD(SLC)</sub> | 140 | SLC output digital supply voltage                                 |

| CKEXT                 | 141 | external clock input                                              |

| COAST                 | 142 | PLL coast control input                                           |

| VSYNC2                | 143 | vertical synchronization pulse input 2                            |

| VSYNC1                | 144 | vertical synchronization pulse input 1                            |

TDA8754

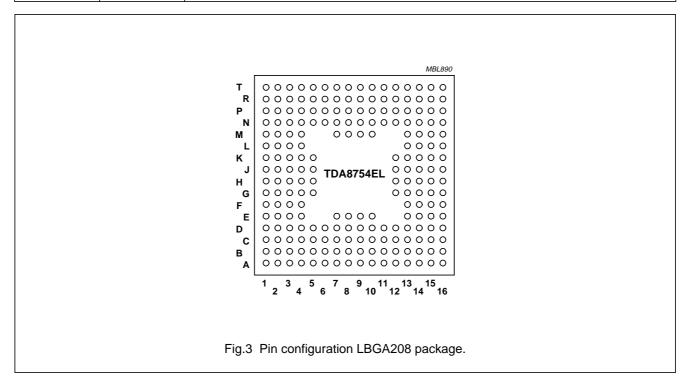

#### 7.2 LBGA208 package

| SYMBOL                | BALL | DESCRIPTION                                                       |

|-----------------------|------|-------------------------------------------------------------------|

| SOGIN1                | A1   | sync-on-green input 1                                             |

| GNDA(PLL)             | A2   | PLL analog ground                                                 |

| SOGIN2                | A3   | sync-on-green input 2                                             |

| GNDA(PLL)             | A4   | PLL analog ground                                                 |

| HSYNC2                | A5   | horizontal synchronization pulse input 2                          |

| CHSYNC2               | A6   | composite horizontal synchronization pulse input 2                |

| COAST                 | A7   | PLL coast control input                                           |

| CSYNCO                | A8   | composite synchronization output                                  |

| FIELDO                | A9   | field information output                                          |

| HSYNCO                | A10  | horizontal synchronization pulse output                           |

| SCL                   | A11  | I <sup>2</sup> C-bus serial clock input                           |

| n.c.                  | A12  | not connected                                                     |

| n.c.                  | A13  | not connected                                                     |

| DIS                   | A14  | I <sup>2</sup> C-bus disable control input                        |

| A0                    | A15  | I <sup>2</sup> C-bus address control input                        |

| CKDATA                | A16  | data clock output                                                 |

| GNDA(PLL)             | B1   | PLL analog ground                                                 |

| PMO                   | B2   | phase measurement output (test)                                   |

| GNDA(PLL)             | В3   | PLL analog ground                                                 |

| GNDA(PLL)             | B4   | PLL analog ground                                                 |

| V <sub>CCA(PLL)</sub> | B5   | PLL analog supply voltage                                         |

| CLP                   | B6   | clamp pulse input                                                 |

| CKEXT                 | B7   | external clock input                                              |

| CKREFO                | B8   | reference output clock; re-synchronized horizontal negative pulse |

| VSYNCO                | B9   | vertical synchronization pulse output                             |

| DEO                   | B10  | data enable output                                                |

| SDA                   | B11  | I <sup>2</sup> C-bus serial data input and output                 |

| n.c.                  | B12  | not connected                                                     |

| n.c.                  | B13  | not connected                                                     |

| n.c.                  | B14  | not connected                                                     |

| GNDO(CLK)             | B15  | clock output digital ground                                       |

| V <sub>CCO(CLK)</sub> | B16  | clock output digital supply voltage                               |

| RIN1                  | C1   | red channel analog input 1                                        |

| GNDA                  | C2   | analog ground                                                     |

| CAPSOGIN1             | C3   | decoupling SOG input 1                                            |

| CAPSOGIN2             | C4   | decoupling SOG input 2                                            |